If the address is sent to the address on the bus, the device is addressed by the master device, Receive information or transmitting information is determined by the 8th (R / W). The format is as follows:Īfter starting the signal, each device in the system is sent to the address of your address and the main device to the bus. The direction is "0" means that the transmission, that is, the main device writes the information to the selected slave device the direction bit is "1" indicates that the master will read information from the slave device. The data transfer format of the IIC bus is after the IIC bus start signal, the first byte data sent is used to select the slave device address, where the first 7 is the address code, the 8th is the direction bits (R / W). 9 pulses are required for each byte, and the number of bytes per transmit is unrestricted. In line with, the master generates 8 pulses on the SCL line the 9 pulse low level, the transmitter releases the SDA line, and the receiver pulls the SDA line to give a reception confirmation bit 9th pulse During the high level, the transmitter receives this confirmation bit and starts the next byte transmission, and the next byte of the first pulse low level receiver releases SDA.

MODELSIM ALTERA 9.0 SERIAL

The IIC bus data transmission uses clock pulses to line up a serial transmission method, during the low level of SCL, high, low power energy changes, during high level, data, must be stabilized so that the receiver sampling Receive, the timing is shown in Figure 2.Įach byte of the IIC bus transmitter is sent to the SDA line must be 8-bit long, and the high position is before, the low is behind. After a period of time, the bus is considered to be idle. The main device exits the main device role after the end signal. After starting the signal, the bus is considered to be busy, and other devices can no longer generate start signals. Starting and end signals are generated by the master. Start signal: When the clock bus SCL is high, the data line SDA is hopped by a high level to a low level and start transmitting data.Įnd Signal: When the SCL line is high, the SDA line hipss from the low level to high and end the transfer data. In the IIC bus technology specification, the definition of start and end signals (also known as start and stop signals) are shown in Figure 1. 2、IIC Bus transfer protocol and data transfer timing (1) Start and stop conditionsĭuring the data transfer, you must confirm the start and end of the data transfer. The number of interfaces connected to the bus is only 400 pF. The transmission rate of data on the IIC bus can reach 100kbit / s in the standard mode up to 400kbit / s up to 3.4 Mbit / s in high speed mode. It can be seen that the clock low level time is determined by the device with the longest time period of the clock, and the clock high level time is determined by the shortest device for the shortest level of the clock. This creates a synchronous clock on the SCL line. Thereafter, the first device ends the high-level device pulls the SCL line into a low level.

When all the clock signals of all devices become high, the low level is ended, the SCL line is released to return to a high level, that is, all devices start their high levels at the same time. At this time, the clock of the device shorter short period is not affected by the low-to-high hopping does not affect the state of the SCL line, which will enter a state in which the high level is waiting. Once a device's clock signal becomes low, all devices on the SCL are started and low-level. The hop on the SCL line from a high level to a low will affect these devices. The clock synchronization signal when transmitting information on the IIC bus is done by logic "and" that are hooked on all devices on the SCL clock line. Third, experimental principle 1、 IIC Bus device working principle

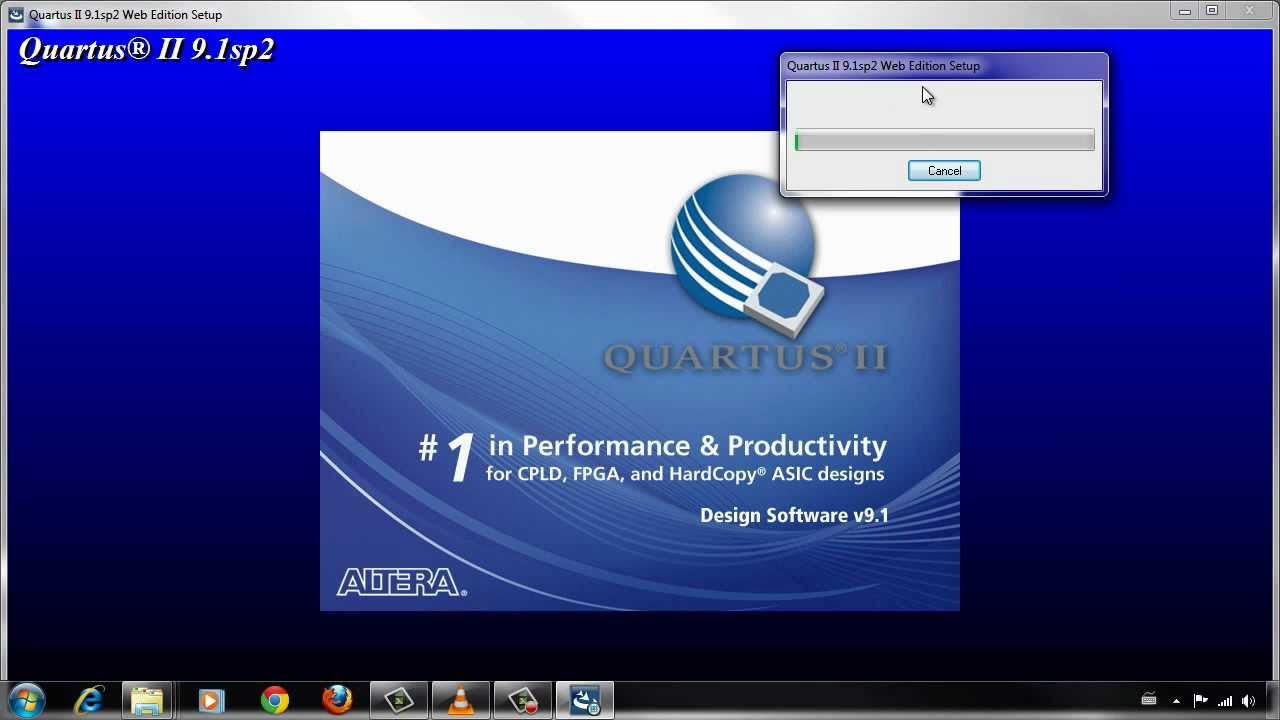

MODELSIM ALTERA 9.0 SOFTWARE

Software Platform: Modelsim-Altera 6.4A (Quartus II 9.0) In DE2_TV, the method for the configuration of the register is the function of IIC, here is described here to make a description of the FPGA of the IIC bus.

0 kommentar(er)

0 kommentar(er)